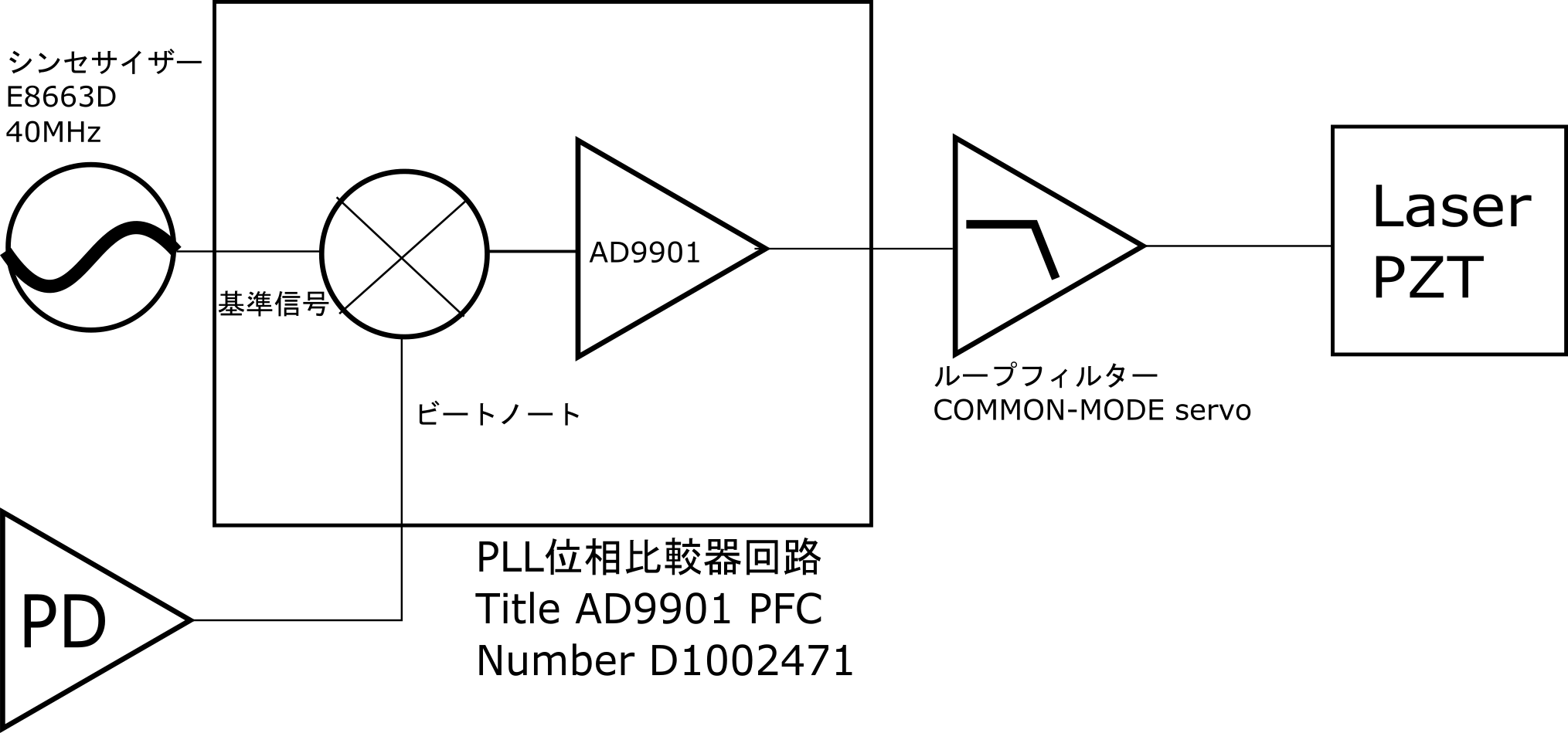

PLL system

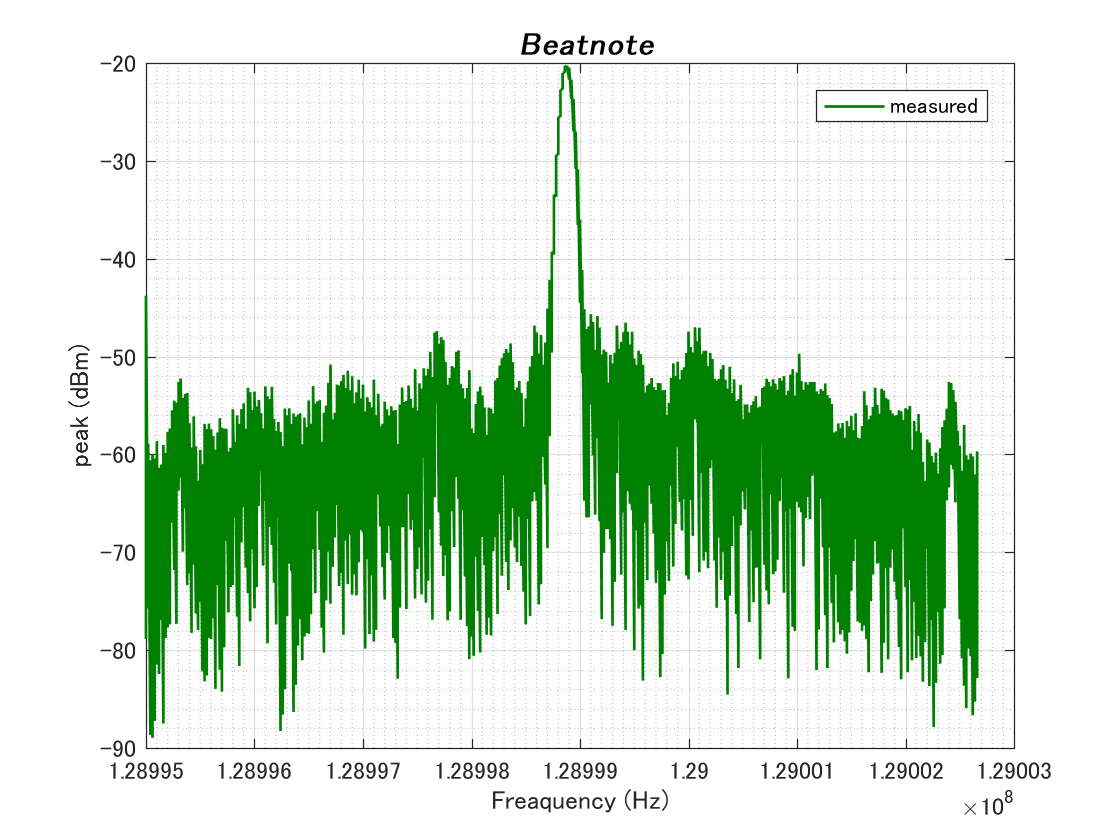

129MHzのところでPLLロックしたときのビート。中心周波数は128998860Hzで、半値全幅は120Hz

問題点

中心の周波数が129MHzから1.1kHzずれている128998860Hzのところにある。

ロックしたときのフロアレベルが高い

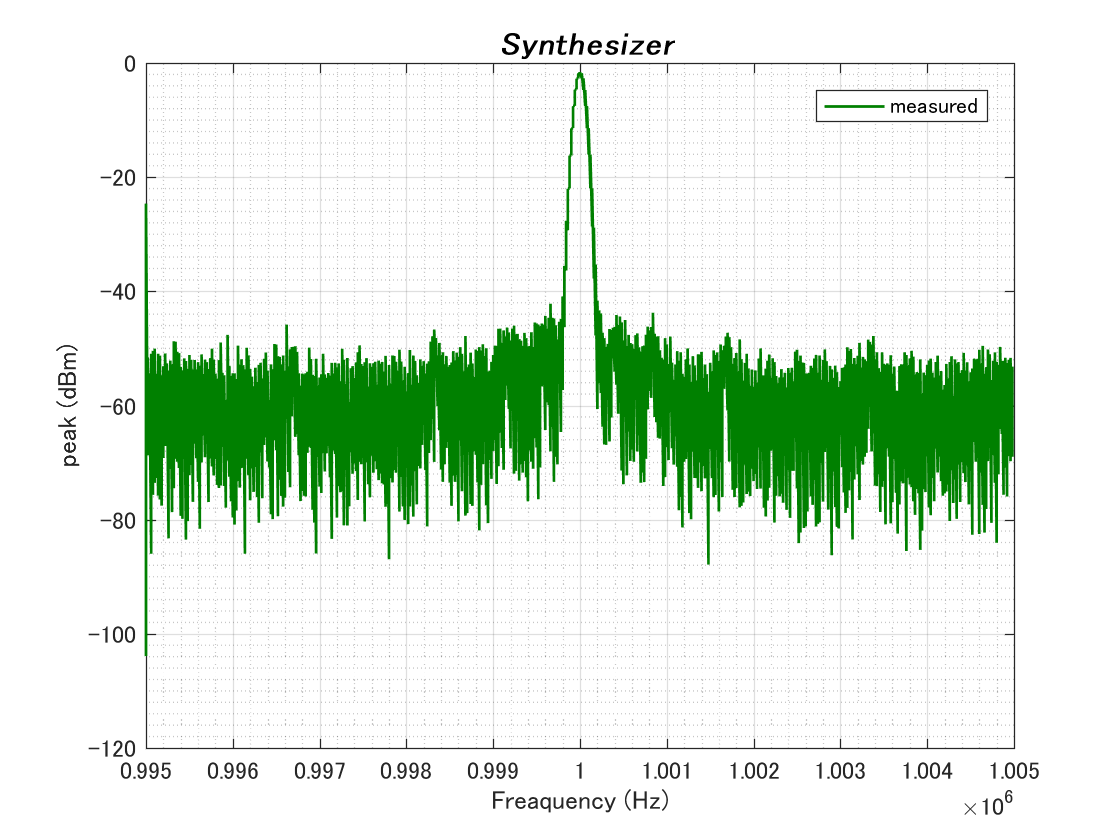

基準信号

中心周波数1000000Hz、半値全幅80Hz

基準信号が原因ではないと思う。(シンセサイザーはTEXIOのやつ)

ロックしたときのコントロールシグナル

このときは7.5分間ロックした

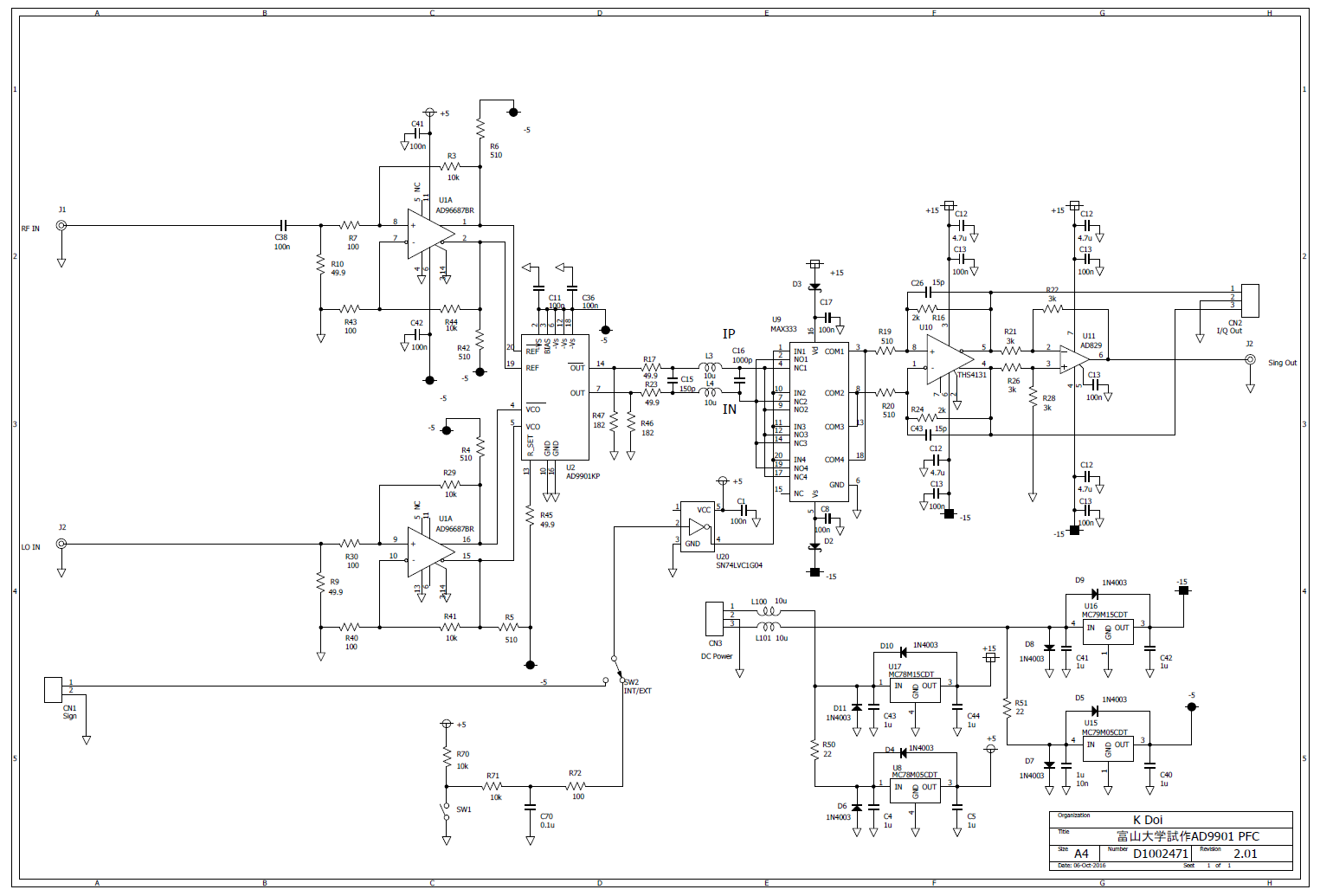

プロトタイプPLL

LIGOのD1002471から,Log detectorやRFアンプを排除したPFCを下に示す.Loop-filterに相当する部分は含まれていない.

PLL回路のオーバービュー