|

Size: 226

Comment:

|

Size: 417

Comment:

|

| Deletions are marked like this. | Additions are marked like this. |

| Line 3: | Line 3: |

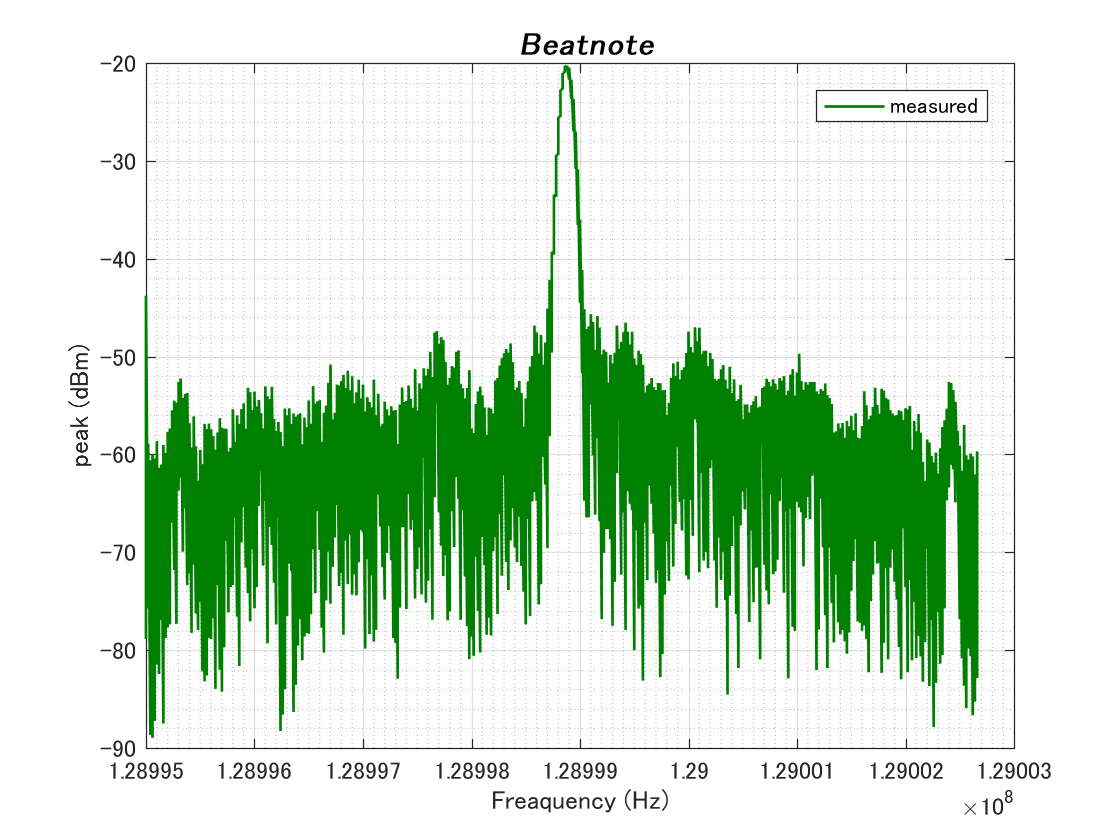

| 129MHzのところでPLLロックしたときのビート | 129MHzのところでPLLロックしたときのビート。中心周波数は128998860Hzで、半値全幅は120Hz |

| Line 7: | Line 7: |

| 中心の周波数が129MHzから1.3kHzずれている | 中心の周波数が129MHzから1.1kHzずれている128998860Hzのところにある。 |

| Line 9: | Line 9: |

| フロアレベルが高い | ロックしたときのフロアレベルが高い |

| Line 12: | Line 12: |

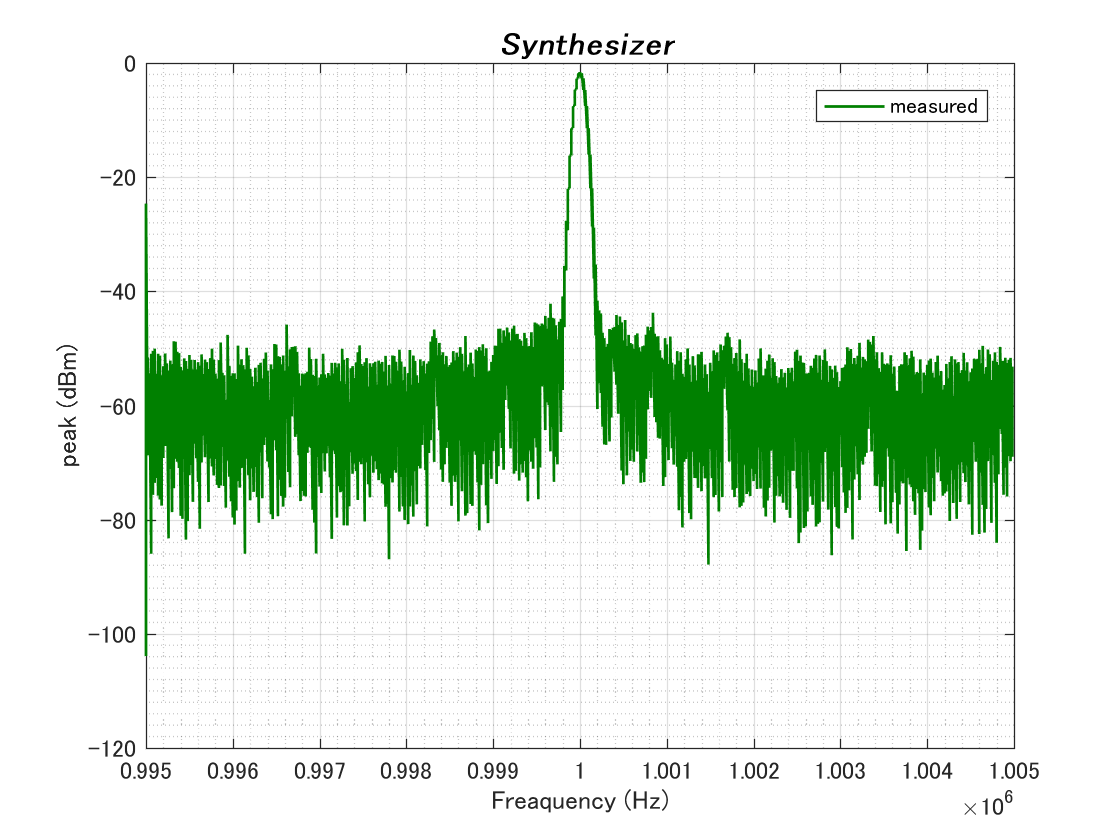

基準信号 {{attachment:16シンセ.bmp|Beatnote|width="1000"}} |

PLL system

129MHzのところでPLLロックしたときのビート。中心周波数は128998860Hzで、半値全幅は120Hz

問題点

中心の周波数が129MHzから1.1kHzずれている128998860Hzのところにある。

ロックしたときのフロアレベルが高い

基準信号